imecが推進するロジック半導体高集積化の鍵を握るBSPDN、その特徴を理解する 第4回 裏面電源供給ネットワークはデバイスの電気的特性を劣化させないか?

2022年10月21日06時55分 / 提供:マイナビニュース![]()

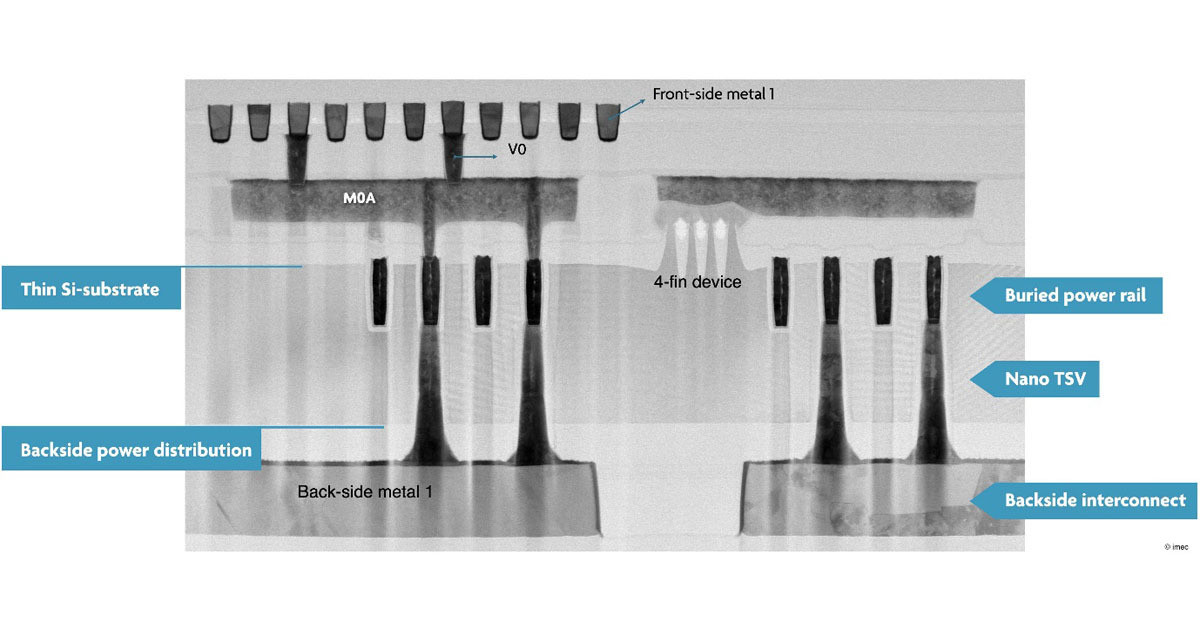

まだ重要な問題が1つ残っている。BPR集積、ウェハ薄化、nTSV形成などの新たに追加されたプロセスステップは、フロントエンドで製造されるデバイスの電気的性能に影響を与えるのではないかという疑問である。

この質問に答えるために、imecは最近、製造フローと上記の改善されたプロセスステップを使用してテストツールを製作した。このテストツールでは、スケーリングされたFinFETが、BPRに着地する深さ320nmのnTSVを介して、厳密なオーバーレイ制御でウェハの裏面に接続される。 BPRは、M0A層とV0ビアを介して前面メタライゼーションにも接続する。とりわけ、この表面接続により、研究者は裏面プロセスの前後でデバイスの電気的性能を評価することができた。imecは、このテストツールを使用して、BPRの実装と裏面処理によってFinFETの性能が低下しないことを確認した。

[ 続きを読む ]

関連記事

- Samsungが2025年に2nm、2027年には1.4nmプロセスでの生産を計画

- TSMCの3nmは2022年後半より量産を開始、日本では大阪に開発拠点設置を計画

- 東工大などがチップレット集積技術「PSB」を開発、コンソーシアムも設立

- TSMC、初の海外開発拠点となる「3DIC研究開発センター」をつくば産総研内に開設

- 半導体洗浄時におけるナノ構造物の倒壊の様子、北大などが詳細観察に成功