imecが推進するロジック半導体高集積化の鍵を握るBSPDN、その特徴を理解する 第1回 次世代ロジックデバイスになぜ裏面電源供給網(BSPDN)が必要なのか?

2022年10月18日07時00分 / 提供:マイナビニュース![]()

ロジックデバイスの超微細化というと、EUV露光やその先の高NA EUV露光を活用した2次元平面回路パターンの比例縮小(スケーリング)やFEOL(Front End of Line)でのトランジスタ構造の変化(プレーナー構造からFinFETを経てGate-All-Around、さらにはCFETへ)ばかりに目が行きがちであるが、トランジスタの超高集積化、つまりトランジスタ密度の増加に対応して、近い将来、BEOL(Back End of Line)の多層配線構造も大きく変わろうとしている。

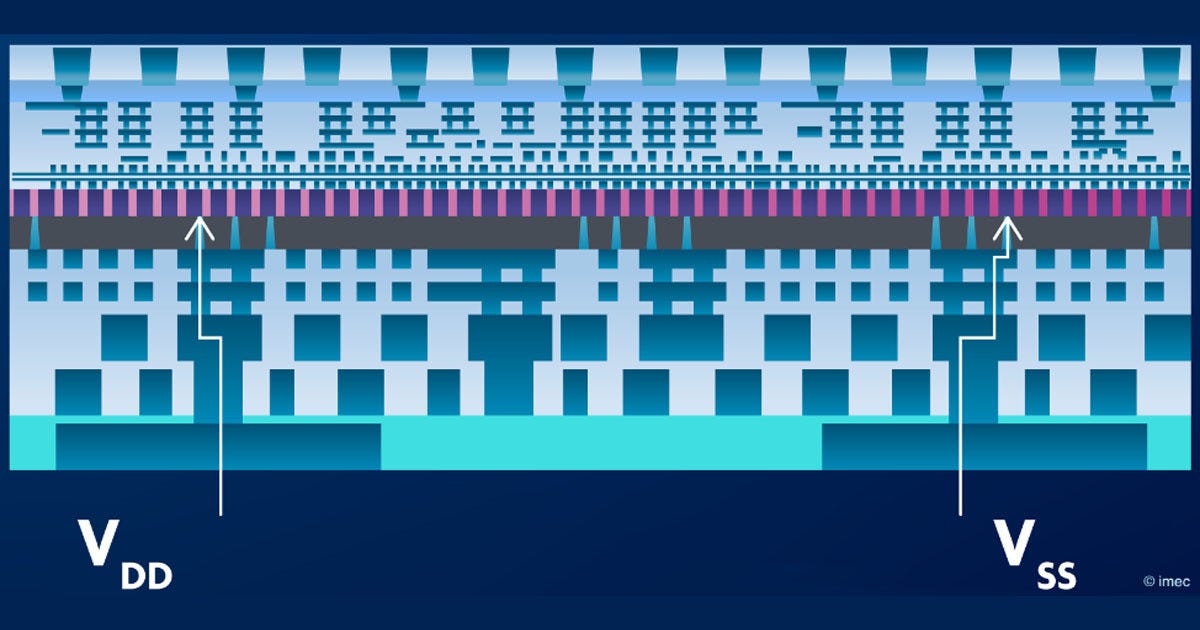

これまでは、トランジスタの上部に多層配線層を形成して電力を供給していたが、集積度が高まるにつれてこれらの電源供給配線網(PDN:Power Delivery Network)が大きな面積を占有し、単位面積当たりのトランジスタ集積度向上の妨げになっていた。このため、電源供給を裏面側から行うことで、前面側の配線設計の柔軟性を高められるようする提案が行われている。この手法はベルギーのimecで盛んに研究されており、米Intelは2nm世代(Intel 20A)から採用すると発表している。ソニーのイメージセンサ(CIS)も以前は、配線層と画素が同居していたが、配線層を下部に分離することで画素の面積を拡大し感度を向上させているのと同じような発想である。ロジックの場合は、配線層を裏面へと分離することにより、トランジスタ密度を上げようとしている。

[ 続きを読む ]

関連記事

- Samsungが2025年に2nm、2027年には1.4nmプロセスでの生産を計画

- TSMCの3nmは2022年後半より量産を開始、日本では大阪に開発拠点設置を計画

- 東工大などがチップレット集積技術「PSB」を開発、コンソーシアムも設立

- TSMC、初の海外開発拠点となる「3DIC研究開発センター」をつくば産総研内に開設

- 半導体洗浄時におけるナノ構造物の倒壊の様子、北大などが詳細観察に成功